# Development of a Novel Readout System for Small Animal Positron Emission Tomography

Diplomarbeit von Jan-Frederik Pietschmann

### Experimentelle Physik

## Development of a Novel Readout System for Small Animal Positron Emission Tomography

Diplomarbeit von

Jan-Frederik Pietschmann

Westfälische Wilhelms-Universität Münster Institut für Kernphysik

— März 2008 —

### Contents

| Ι   | Intro | oduction                                              | 7  |  |  |  |

|-----|-------|-------------------------------------------------------|----|--|--|--|

| II  | Posit | Positron Emission Tomography                          |    |  |  |  |

|     | II.1  | The Principle of PET                                  | 11 |  |  |  |

|     | II.2  | A Short History of PET                                | 15 |  |  |  |

|     | II.3  | Small Animal PET                                      | 16 |  |  |  |

|     | II.4  | Reconstruction Algorithms for PET                     | 17 |  |  |  |

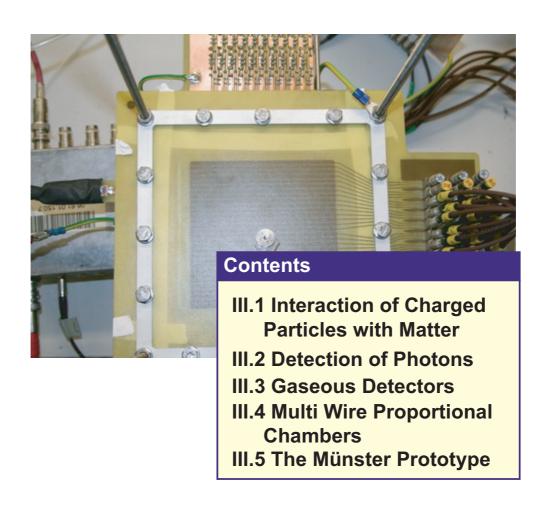

| III | Gase  | eous detectors                                        | 21 |  |  |  |

|     | III.1 | Interaction of charged particles with Matter          | 22 |  |  |  |

|     | III.2 | Detection of Photons                                  | 23 |  |  |  |

|     | III.3 | Gaseous detectors                                     | 24 |  |  |  |

|     |       | III.3.1 Strong Electric Field and Avalanche Formation | 24 |  |  |  |

|     |       | III.3.2 Proportional Counter                          | 24 |  |  |  |

|     |       | III.3.3 Filling Gas                                   | 28 |  |  |  |

|     | III.4 | Multi Wire Proportional Chambers                      | 29 |  |  |  |

|     |       | III.4.1 Electrostatics within a MWPC                  | 31 |  |  |  |

|     |       | III.4.2 Readout and Resolution Recovery               | 31 |  |  |  |

|     | III.5 | The Münster Prototype                                 | 35 |  |  |  |

| IV  | Expe  | erimental Evaluation of the msPET MWPC Prototypes     | 37 |  |  |  |

|     | IV.1  | Event Maps                                            | 38 |  |  |  |

|     | IV.2  | Efficiency                                            | 40 |  |  |  |

|     | IV.3  | Gas Gain and Pulse Heights                            | 43 |  |  |  |

|     |       | IV.3.1 Simulations with Garfield                      | 43 |  |  |  |

6 Contents

|    | IV.4   | Spatia             | l Resolution                                                 | 45 |

|----|--------|--------------------|--------------------------------------------------------------|----|

| V  | The    | n-XYT              | ER Readout Chip                                              | 49 |

|    | V.1    | Interna            | al Layout of the n-XYTER                                     | 50 |

|    |        | V.1.1              | Analog Frontend                                              | 52 |

|    |        | V.1.2              | Digital Part                                                 | 53 |

|    |        | V.1.3              | Slow Control and Test Channel                                | 53 |

|    | V.2    | The n-             | XYTER's Digital Data Output Format                           | 55 |

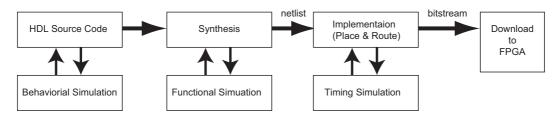

| VI | A R    | eadout             | Board Prototype                                              | 57 |

|    | VI.1   | Field I            | Programmable Gate Arrays                                     | 58 |

|    |        | VI.1.1             | A Short History of Programmable Logic Devices                | 58 |

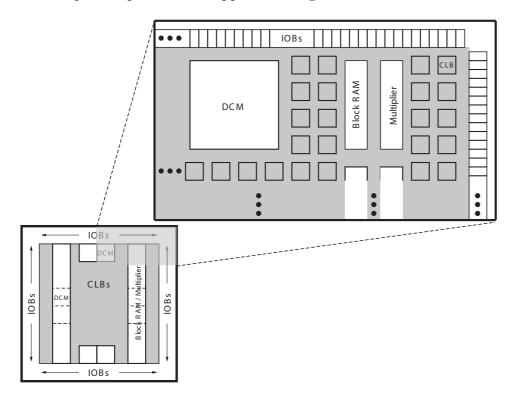

|    |        | VI.1.2             | FPGA Architecture                                            | 61 |

|    |        | VI.1.3             | Hardware Description Languages                               | 61 |

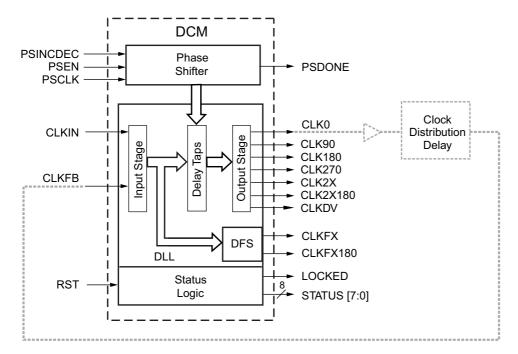

|    |        | VI.1.4             | Xilinx Spartan 3                                             | 64 |

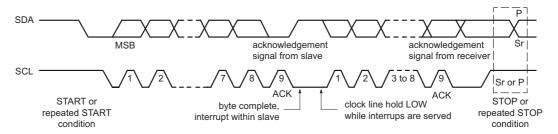

|    | VI.2   | The I <sup>2</sup> | C Bus                                                        | 66 |

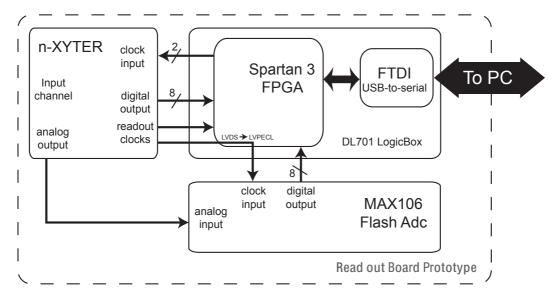

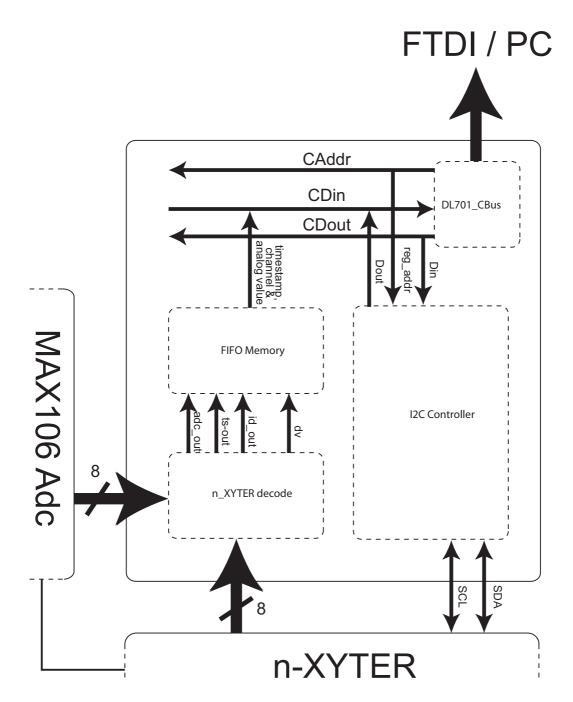

|    | VI.3   | Archit             | ecture of the Prototype                                      | 67 |

|    |        | VI.3.1             | MAX106 Analog To Digital Converter                           | 68 |

|    |        | VI.3.2             | The DL701 LogicBox                                           | 68 |

|    | VI.4   | Sparta             | n 3 Program Design                                           | 69 |

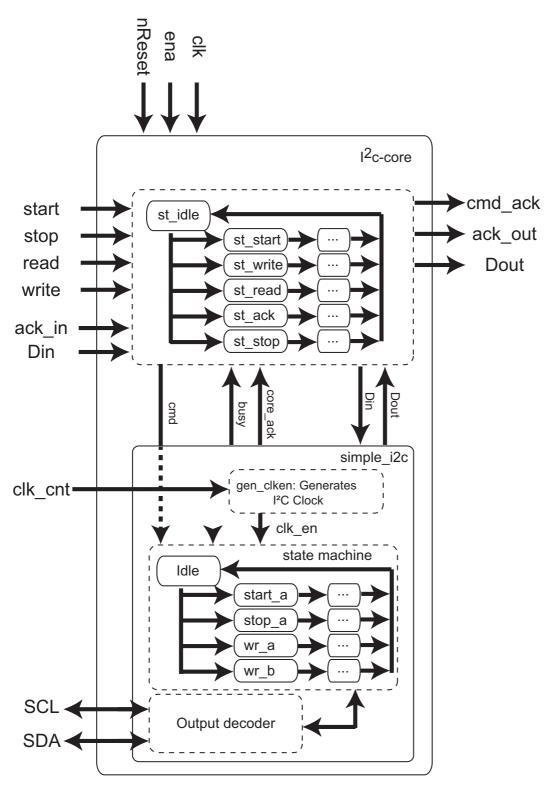

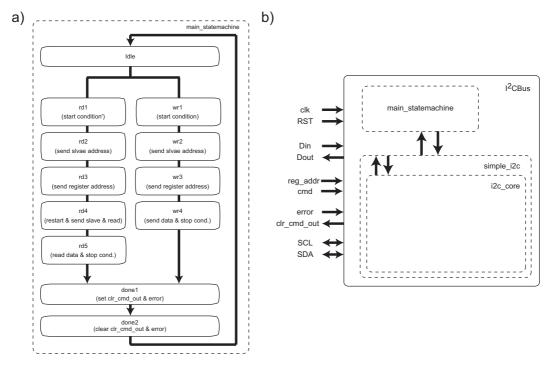

|    |        | VI.4.1             | $I^2C$ -Controller                                           | 69 |

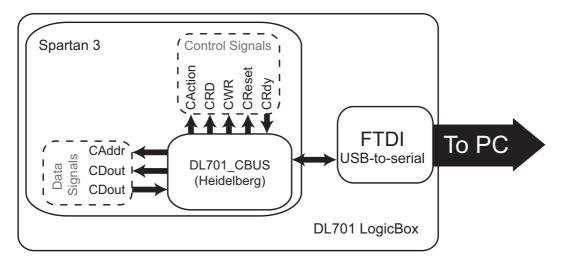

|    |        | VI.4.2             | The DL701_CBus unit                                          | 71 |

|    |        | VI.4.3             | Data Decoding                                                | 72 |

|    |        | VI.4.4             | The Main Program                                             | 73 |

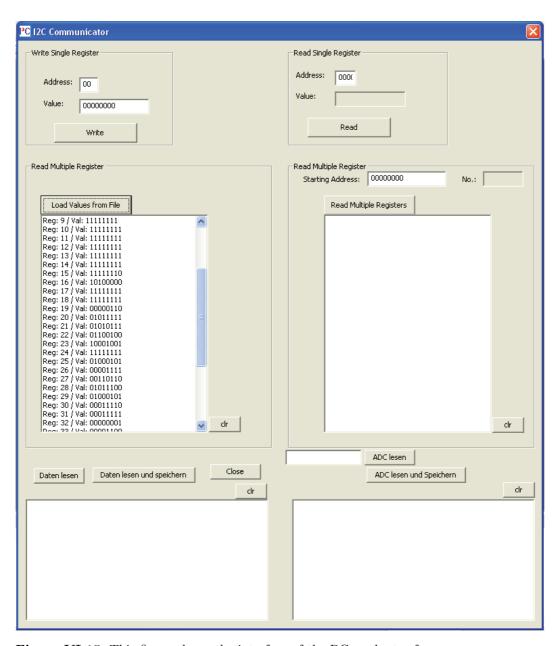

|    | VI.5   | Softwa             | re on the Readout PC                                         | 75 |

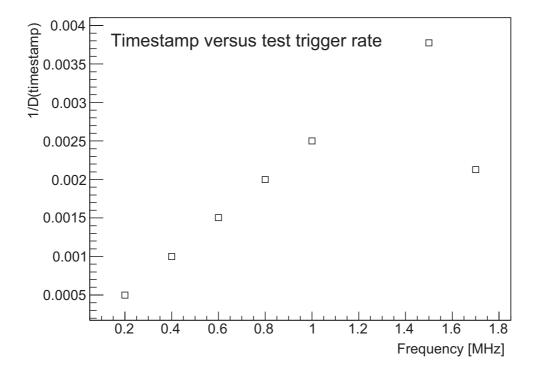

|    | VI.6   | Experi             | mental Test: Timestamp Accuracy Using the Test Trigger Input | 75 |

| VI | ISum   | mary               |                                                              | 79 |

| Bi | bliogr | aphy               |                                                              | 81 |

| Α  | Ackı   | nowledg            | gements                                                      | 85 |

### CHAPTER I

### Introduction

Positron Emission Tomography (PET) is a medical imaging method. Today, PET devices are present in almost every larger hospital. The great advantage of PET compared to Nuclear Magnetic Resonance (NMR) or Computed Tomography (CT) it its ability to visualize functional processes. This makes it popular in oncology and cardio vascular imaging [Tsui05].

As many imaging techniques, PET has also been adapted for small animals likes mice or rats as they are important models in clinical research. Due to their small size compared to humans, dedicated small animal PET scanner with increased spatial resolution and sensitivity have been developed.

At the Münster University Hospital, a quadHIDAC small animal PET scanner is installed. Unlike most other systems, this device is based on Multi Wire Proportional Chambers (MWPC) instead of scintillation crystals. It is used for research within the framework of the Sonderforschungsbereich 656 to examine the cardio vascular system.

However, as support is no longer available for the quadHIDAC device, it has been decided to develop a new small animal scanner prototype, called msPET, also based on MWPCs.

The main task of this thesis was to develop a readout system for this prototype, based on the n-XYTER readout chip. This chip has been developed within the framework of the European project "Detectors for Neutron Instrumentation" (DETNI). However, many of its properties are very suitable for PET. Furthermore, a Spartan 3 Field Programmable Gate Array (FPGA) has been used as a core of the readout

board.

Finally, the performance of the existing MWPC prototypes for msPET has been evaluated. After examining the basic operation of the chambers, tests have been done to determine their efficiency and spatial resolution.

### CHAPTER II

### Positron Emission Tomography

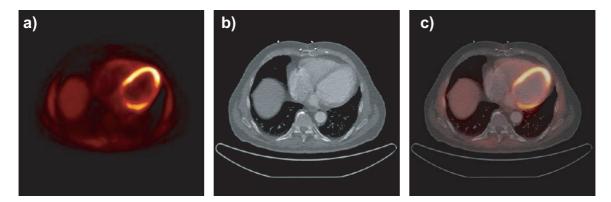

Figure II.1: Images obtained by a) PET only, b) CT only and c) their combination. [Büther07]

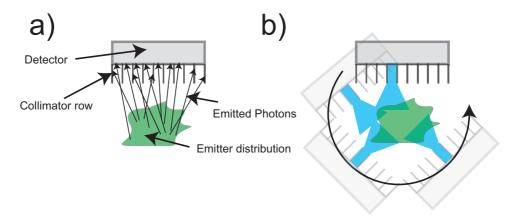

There is a great need in medicine for methods to non invasively image the interior of the human (or animal) body. Emission tomography (ET) is the generic term for all methods that are based on the detection of radiation emitted from radioactive material within the body. The two main representatives of ET are single photon emission computed tomography (SPECT) and positron emission tomography (PET). SPECT is a method which works with virtually every  $\gamma$  emitting substance. As shown in Figure II.2, it uses a collimator in front of a detector to determine the direction of an incoming photon. This leads to a cone on which the decay must have taken place, see Figure II.2 b). By rotating the detector and using appropriate algorithms, it is possible to reconstruct the three dimensional distribution of the radioactive emitter. The principle of PET will be explained in detail in the following sections.

#### The Tracer Principle

One important concept in nuclear medicine is the tracer principle, developed in about 1900 by George de Hevesy [deHevesy48]. It allows the examination of particular biological processes within animals and humans using PET and SPECT. De Hevesy recognized that integration of radioactive isotopes in organic compounds does not alter their biological behaviour. Therefore, radioactively marked biomolecules can be used to trace the concentration of specific substances within the body. This ability to examine functional processes distinguishes emission tomography from computed tomography (CT) or nuclear magnetic resonance tomography (NMR). These methods are only able to visualize the morphology of the tissue. However, as CT usually provides excellent spatial resolution, combinations of PET and CT, known as PET/CT, became very popular in recent years. Images created by PET, CT and their combinations are shown in Figure II.1.

Figure II.2: The principle of single photon computed emission tomography (SPECT).

### II.1 The Principle of PET

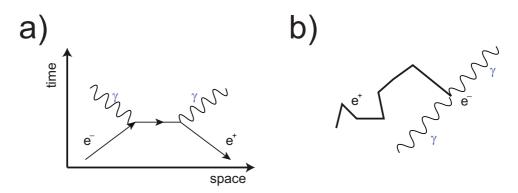

**Figure II.3:** a) One possible Feynman diagram for positron electron annihilation. b) A positron losing its enery in multiple scattering processes and finally performing positron electron annihilation.

Positron Emission Tomography uses photons that are emitted in positron electron annihilations. In this process, two photons are created in the reaction

$$e^+e^- \to \gamma\gamma$$

. (II.1)

This can be expressed in a Feynman diagram as shown in Figure II.3 a). As the reaction results in two identical bosons, another diagram with photons switched must be considered. Using these diagrams, it is possible to calculate the cross section of positron electron annihilation. As it is very tiny (at high kinetic energies T it behaves like ln(T)/T) [Lohrmann86], most positrons are slowed down until they practically have a velocity of zero. Then, they form a bound state with the electron which is

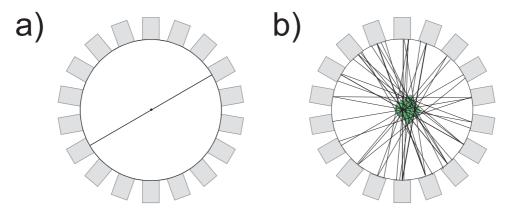

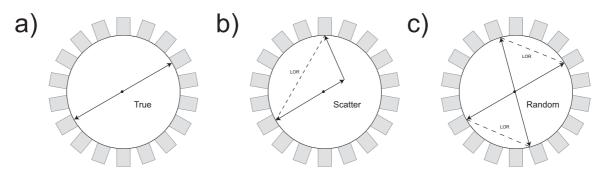

called positronium before they finally annihilate. This is shown in Figure II.3 b). According to the law of energy conservation, the photons must have the energy of the electron and the positron. Therefore, they both most likely have a energy of 511keV. The important fact for PET is that the two 511 keV  $\gamma$  photons are emitted back to back. Detecting these photons in coincidence results in a line on which - neglecting the effects of the positron range - the decay must have taken place (Figure II.4, a). This line is commonly called *line of response* (LOR). It is obvious that the detection several of these lines increases the information about the distribution of the emitting element tremendously, as shown in Figure II.4 b). Using appropriate reconstruction

**Figure II.4:** a) A single line of response created by two 511 keV  $\gamma$  photons. b) Same situation for an extended source. Note that in practice, the coordinates of the detected photons are set to be in the middle of the szintillation crystals.

algorithms it is possible to reconstruct a three dimensional map of the sites of decay. In medical applications, the positrons needed for the annihilation are created by a  $\beta^+$  isotope in the reaction

$$_{Z}^{A}X \to_{Z-1}^{A}X + e^{+} + \nu_{e}.$$

(II.2)

Compared to the detection of single photons in SPECT, coincidence measurements in PET allow a more accurate localisation of the decay. Furthermore, in PET far more of the emitted photons are used as it covers a greater solid angle. Each coincidence results in a line on which the decay must have taken place. In SPECT, each measurement only results in a cone. However this also introduces additional problems: If one of the photons is scattered (either on its way to or within the detector itself) the LOR does not intersect the real decay site. Events of this type are called "scattered events", this phenomena is shown in Figure II.6 b). The second

**Figure II.5:** The tracks of positrons emitted by  $^{18}$ F in water. 100 tracks have been simulated. [Levin99]

**Figure II.6:** a) A "true" coincidence. b) A "scattered" event. c) A "random" event. The dashed line indicates the measured line of response.

possible error occurs if two annihilations take place almost or completely simultaneously. Then, two photons emitted by different annihilations may accidentally be detected in coincidence. This also leads to a wrong LOR and is schematically shown in Figure II.6 c). Such events are commonly called "random events". Both effects decrease the spacial resolution. They are also major problems for quantitative PET. Recent approaches try to estimate the scatter and random fraction by use of Monte Carlo simulations and adapt the reconstruction algorithms to correct them [Gottschlag07, Kösters07]. In PET, the set of possible tracers is of course limited

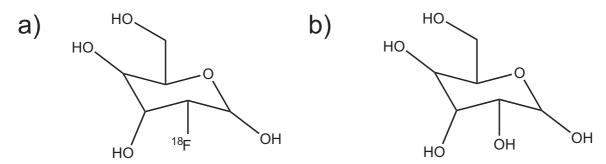

Figure II.7: a) <sup>18</sup>F-FDG. b) Ordinary glucose.

to  $\beta^+$  emitter as only they create positrons. The most popular tracer in clinical PET applications today is <sup>18</sup>F-fluorodeoxyglucose (<sup>18</sup>F – FDG). In <sup>18</sup>F – FDG one of the OH groups of ordinary glucose is replaced by a <sup>18</sup>F. <sup>18</sup>F – FDG enters a cell in the same way as usual glucose does. However, within the cell it is metabolized to a new compound that remains in its interior. This leads to an increasing concentration of <sup>18</sup>F, growing proportionally to the cells glucose metabolic rate [Wernick04]. Furthermore, <sup>18</sup>F has a half life of

$$t_{1/2} = 109.77 \text{ min},$$

which means that it exists long enough to perform an examination but does not remain very long in the patient's body afterwards. The chemical structure of  $^{18}\text{F} - \text{FDG}$  and ordinary glucose are shown in Figure II.7.

#### Commercially available devices

Commercial PET scanners are either based on scintillation crystals or on gaseous detectors. Scintillation scanners are more often used in practice. This is due to the fact that they are very reliable. For devices based on scintillation crystals, the spacial resolution basically depends on the size of the crystals. This means that decreasing

the crystal size in order to obtain a higher spacial resolution, the number of crystals raises if the solid angle coverage is constant. As every crystal needs additional readout electronics and the crystals themselves are expensive, this increases costs of such a scanner. On the other hand, scanners based on gaseous detectors have a greater spatial resolution and are much cheaper. They can provide an intrinsic resolution on the order of 1 mm or even better [Ott93].

### II.2 A Short History of PET

The whole principle of PET is based on the discovery of the positron. This particle was postulated by P. Dirac<sup>1</sup> in 1928. In 1932, Carl Anderson<sup>2</sup> was able to experimentally find it in cosmic rays, using a cloud chamber [Anderson33]. He also gave it its name. Furthermore, he predicted the existence of positronium (also in 1932). It was experimentally discovered by Martin Deutsch<sup>3</sup> in 1951 [Deutsch51].

Even though the first imaging devices did not appear until 1940, there were a number of simpler applications beforehand. One of the earliest examples is the examination of the thyroid using radioactive substances. In the first simple approaches, a short lived iodine isotope was applied to the patient. Then, a map of the intensity distribution of the emitted  $\gamma$  rays was produced either by hand or using a dot tapper. An early image is shown in Figure II.8. In the mid- to late 1940s, the first clinical imaging devices were developed. They were based on Na(I)Tl scintillation crystals that were coupled to a motor driven system. Some of these devices already used a pair of opposite detectors. They contained an electronic coincidence circuit and were thus the first real PET devices. The first clinical PET scanner was built in 1952 by Brownell and Aranow [Brownell99].

In 1960, the first cyclotron dedicated to the production of isotopes needed for medical imaging was installed at the Hammersmith Hospital in London. Thenceforward, PET and other techniques based on emission tomography became more and more

<sup>&</sup>lt;sup>1</sup>Paul Adrien Maurice Dirac was a British theoretical physicist. He was born August 8, 1902 in Bristol and died October 20, 1984 in Tallahassee. In 1933 he received the Nobel price "for the discovery of new productive forms of atomic theory".

<sup>&</sup>lt;sup>2</sup>Carl David Anderson was a US American physicist. He was born 3 September 1905 in New York and died 11 January 1991 in San Marino, California. In 1936, the received the Nobel price "for his discovery of the positron".

<sup>&</sup>lt;sup>3</sup>Martin Deutsch was an Austrian-American physicist. He was born on 29 January 1917 in Vienna and died 16 August 2002 in Cambridge, Massachusetts.

**Figure II.8:** a) Image produced with an experimental early imaging device. The picture has been recorded using a dot tapper. [Andrews62]. b) The first clinical PET device, developed in 1952 by Brownell and Aranow [Brownell99].

popular in clinical practice. Today, PET and SPECT are standard examinations in almost every larger hospital.

### II.3 Small Animal PET

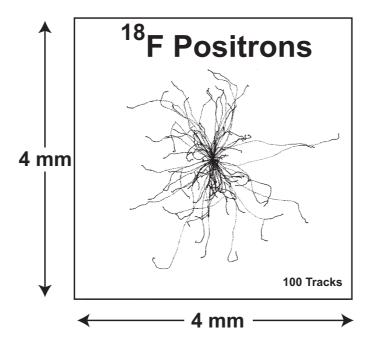

As other imaging methods like CT, PET has been adapted for the use in animal experiments. In case of PET there are some limitations concerning small animals such as mice or rats. Typical human scanners today provide a resolution of about 4 to 10 mm in clinical practice, specialized brain scanners achive up to 2 mm [Schäfers08]. The average mass of a mouse (rat) is 30 g (300 g). Compared to an average human with 70 kg, this is a factor of about 200 to 2000 in mass and thus volume. To achive comparable image quality and be able to examine the same biological questions, the spacial resolution of a dedicated small animal PET scanner must be about 1 mm. As the avarage range of positrons within tissue is also about 1 mm [Levin99], this sets a fundamental limit for the spacial resolution in PET.

Furthermore, small animal PET makes great demands on the sensitivity of the scanner. Sensitivity refers to the fraction of emitted  $\gamma$  photons that are detected by the scanner. This is an important quantity as the number of decays detected per voxel is proportional to the signal to noise ratio of the measurement and thus in the resulting image. As the voxelsize in small animal PET ( $\sim \mu$ l) is much smaller

than in human PET ( $\sim$  ml), a better sensitivity is needed to compensate this effect. The relative reduction in sensitivity can partly be compensated by using a greater tracer concentration within the animals. However, the maximum concentration is still limited as it must not disturb the biological process that is examined in the experiment.

Considering all these criteria, a number of dedicated small animal scanners has been developed. Most of them are based on scintallation crystals. Their spacial resolution ranges from 1.8 to 2.1 mm. There is also one device available based on multi wire proportional chambers. It has a spatial resolution of about 1.2 mm.

For a short review on small animal scanners see [Wernick04].

### II.4 Reconstruction Algorithms for PET

The standard method for reconstruction in computed tomography (CT) is the filtered back projection (FBP, for details see [Natterer01]). Even though this method is also applicable to PET, most of the newer devices use iterative algorithms. They produce better results because they take into account the statistical nature of the data.

In this model, the distribution of the tracer within the object is interpreted as a density function

$$f: \mathbb{R}^N \to \mathbb{R}^+, \qquad N = 2, 3.$$

(II.3)

Assuming a discrete set of possible lines of response, the number of events measured per line is the integral of f over this line:

$$\int_{L_i} f(x)dx \approx g_i, \qquad i = 1, \dots, m.$$

(II.4)

As the  $g_i$  are discrete numbers, this equation holds only approximately. The integral is known as Radon<sup>4</sup> transformation. In the next step, a grid is placed over the region of interest and it is assumed that f is constant in every pixel or voxel respectively. The value of f in pixel  $P_i$  is called  $f_i$ . Defining  $a_{ij}$  as the length of the intersection of line  $L_i$  with pixel  $P_j$ ,

$$g_i = \sum_{j=1}^n a_{ij} f_j \tag{II.5}$$

$<sup>^4</sup>$ Johann Karl August Radon was an Austrian mathematician. He was born December 16, 1887 in Decin and died May 25, 1956 in Vienna.

holds. With the further definitions

$$A = \begin{pmatrix} a_{11} & \cdots & a_{1n} \\ \vdots & & \vdots \\ a_{m1} & \cdots & a_{mn} \end{pmatrix}, \quad g = \begin{pmatrix} g_1 \\ \vdots \\ g_n \end{pmatrix},$$

equation II.4 can be rewritten as

$$Af = g. (II.6)$$

In principle, every algorithm for solving linear systems of equation could be used to determine f. However as already mentioned, it is advantageous to consider the statistical nature of the  $g_i$ . As radioactive decay is a Poisson-distributed process, it is reasonable to assume that the number of photons that is emitted from pixel  $P_j$  and that are registrated on line  $L_i$ ,  $X_{ij}$  are also Poisson-distributed. From this follows that the number of photons, emitted from every pixel that intersects with line  $L_i$ ,

$$\gamma_i := \sum_{j=1}^n X_{ij} \quad i = 1, \dots, m,$$

(II.7)

is Poison distributed as well. Therefore the measured data  $g_i$  can be interpreted as expectation of the random variable  $\gamma_i$ . To calculate the expectation value it is assumed the matrix element  $a_{ij}$  corresponds to the probability that a photon is registrated on line  $L_i$  under the condition that is was emitted in pixel  $P_j$ . Then,

$$E(\gamma_i) = \sum_{j=1}^{n} a_{ij} f_j = (Af)_i, \quad i = 1, \dots, m$$

(II.8)

holds. The probability for the measured values is then

$$P_f(g_i) = \frac{(Af)_i^{g_i}}{g_i!} e^{-(Af)_i}, \quad i = 1, \dots, m.$$

(II.9)

The idea is now to variate f until the probability matches the measured values best. Formally, this is done by writing the probability as a function of f. This function is called the Likelihood function

$$L(f) := P_f(g) = \prod_{i=1}^m \frac{(Af)_i^{g_i}}{g_i!} e^{-(Af)_i} = g \cdot (Af) - (Af) \cdot 1.$$

(II.10)

To find the maximizer f, it is easier to consider the log-likelihood function. As the logarithm is a monotonic function, it has its maximum at the same place.

$$l(f) := \log L(f) = \sum_{i=1}^{m} (g_i \log(Af)_i - (Af)_i)$$

(II.11)

As the log-likelihood function is convex [Natterer01] is has a unique global maximum. f is this maximum, if the Kuhn-Tucker conditions are fulfilled. This is equal to the fact that f times the gradient of l vanishes, i.e.

$$f\nabla l(f) = fA^T \left(\frac{g}{Af} - 1\right) = 0.$$

(II.12)

Here, 1 is a vector with only 1's and all operation are meant componentwise. Normalizing A so that each column sum is one (or  $A^{T}1 = 1$ ) one gets

$$f = fA^T \frac{g}{Af}. (II.13)$$

The easiest iterative algorithm to solve this equation would then be

$$f^{k+1} = f^k A^T \frac{g}{Af^k}, \quad k = 0, 1, \dots$$

(II.14)

This algorithm is commonly called the EM algorithm. As its convergence is in general very slow, normally the events are subdivided into so-called subsets. This leads to the ordered subset expectation maximization (OSEM) algorithm that is commonly used today. For more detail on OSEM and its implementation see [Hudson94].

### CHAPTER III

### Gaseous detectors

Gaseous detectors are based on the interaction between an incident particle and a gas volume within the detector. There is an extended theoretical framework which provides cross sections and thus probabilities for such interactions. As this is the basis for every detector design, it will be considered first in this chapter. In the latter particular types of gaseous detectors will be described in detail. Beginning with simple proportional counters, multi wire proportional chambers will be explained, especially the Münster MWPC (msPET) prototype chamber.

# III.1 Interaction of charged particles with Matter

If a charged particle traverses matter, it can interact with it via electromagnetic interactions. This principle it is commonly used for the detection of charged particles particles. In the following, we will only deal with the incoherent Coulomb scattering, as done in [Sauli77].

An important quantity in this context is the average energy loss within the traversed matter. This can be described by the famous Bethe<sup>1</sup>-Bloch<sup>2</sup> equation [Bethe<sup>30</sup>, Bloch<sup>33</sup>]. Approximately

$$-\frac{dE}{dX} = \frac{4\pi}{m_e c^2} \frac{nz^2}{\beta^2} \left(\frac{e^2}{4\pi\epsilon_0}\right)^2 \left\{ \ln \frac{2m_e c^2 \beta^2}{I \cdot (1 - \beta^2)} - \beta^2 \right\}, \qquad \beta = \frac{v}{c}$$

(III.1)

holds [Povh04]. In this formula,  $m_e$  and e are electron mass and charge respectively. ze is the charge of the particle, I is the medium's effective ionisation potential. It is obtained by measurements and, in most cases  $I = I_0 Z$  is a good approximation. v is the velocity of the incoming charged particle. The first important thing to see is that the energy loss depends on the velocity and the charge of the transversing

<sup>&</sup>lt;sup>1</sup>Hans Albrecht Bethe was a German-American physicist. We born on Juli 2nd, 1906 in Strasbourg, Alsace-Lorraine and died on March 6, 2005. In 1967, he obtained the Nobel price in physics for "for his contributions to the theory of nuclear reactions, especially his discoveries concerning the energy production in stars"

<sup>&</sup>lt;sup>2</sup>Felix Bloch was a Swiss physicist. He was born on October 23, 1905 and died September 10, 1983. He obtained the Nobel price in 1952, together with Edward Mills Purcell "for their development of new methods for nuclear magnetic precision measurements and discoveries in connection therewith"

particle but not on its mass. In general, the energy loss is normalized to the density  $\rho$  of the transversed matter, introducing a reduced length x so that

$$\frac{dE}{dx} = \frac{1}{\rho} \frac{dE}{dX} \tag{III.2}$$

holds. A qualitative look at equation III.1 shows that the energy loss is dominated by the  $\beta^{-2}$  term for small velocities. At relativistic energies, it increases due to the logarithmic term. These two competing terms lead to a minimum or an almost constant region for the energy loss as a function of projectile energy. This region is called the minimum ionizing region and is the probable case in particle physics [Sauli77].

### III.2 Detection of Photons

As described above, in PET two  $\gamma$  photons with an energy of 511 keV each are emitted. The task of a PET camera is therefore to detect these photons with a maximum efficiency and spatial resolution. Unfortunately, these photons cannot be detected directly with a MWPC as their interaction probability with the gas volume is too low. Therefore, they are converted to electrons first. This is done in a so-called "converter" material that is located directly on the pad planes. There are three different processes of interaction of a photon with matter that lead to the liberation of a electron. These are photoelectric absorption, compton scattering and pair production (for details on these processes, see [Leo87]). However, if the cross-section of all these processes is put together a formula for the overall attenuation of a photon beam can be given as

$$I = I_0 e^{-\sigma NX} = I_0 e^{-\mu x}, \tag{III.3}$$

where  $\sigma$  is the cross-section,  $\mu$  the mass attenuation coefficient and  $x = \rho X$  is the reduced thickness of the medium. This formula can also be written as

$$I = I_0 e^{-(\frac{\mu}{\rho})\rho X}. (III.4)$$

The quantity  $\mu/\rho$  is called "mass attenuation coefficient". Finally, defining the mean free path  $\lambda$  of the particle as  $\lambda = (\mu\rho)^{-1}$ , equation

$$I = I_0 e^{-\frac{X}{\lambda}} \tag{III.5}$$

holds. As the cross section increases with the atomic number, a good choise for the converter is gold (Z = 79) or lead (Z = 82).

### III.3 Gaseous detectors

In the case discussed, the medium in which ionization takes place is always a gas volume. Therefore, diffusion and drift of electrons in gases are important processes. Of special interest is the case of a electric field applied over the gas volume that leads to a net movement of electrons and ions.

### III.3.1 Strong Electric Field and Avalanche Formation

If a electric field is applied over the gas volume that exceeds a certain value, a electron can gather enough energy to ionize gas molecules. The resulting electrons can cause further ionization and thus a so-called "avalanche" is created. Knowing the mean free path of electrons for secondary ionization  $\alpha$ , a formula for the number of electrons created per length can be derived. The inverse of  $\alpha$ , the probability of a ionization per unit length, is often called the "first Townsend<sup>3</sup> coefficient". Starting with n electrons,

$$dn = n\alpha dx \tag{III.6}$$

further electrons will be created. Integration of this formula leads to

$$n = n_0 e^{\alpha x}. (III.7)$$

From a given number of initial electrons, the multiplication factor or gas gain (after a way of length x) is<sup>4</sup>

$$M = \frac{n}{n_0} = e^{\alpha x}. (III.8)$$

As this quantity is a very important parameter for a proportional counter, many models for  $\alpha$  in different gases have been developed. For a review, see [Kowalski85].

### III.3.2 Proportional Counter

Considering all the facts mentioned above, a simple gas detector setup could consist of two parallel, planar plates. In this case, the space between the plates is filled with gas and a electric field is applied. In a charged particle transverses the gas volume,

<sup>&</sup>lt;sup>3</sup>John Sealy Edward Townsend was a Irish physicist. Be was born June 7, 1868 in County Galway, Irland and died February 16, 1957 in Oxford.

<sup>&</sup>lt;sup>4</sup>In the more general case of a non-uniform electric field,  $\alpha$  is a function of x and  $M = exp\left(\int_{r_1}^{r_2} \alpha(x)dx\right)$  holds instead.

III.3 Gaseous detectors 25

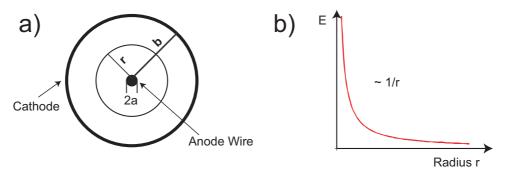

it causes ionization. Due to the electric field, the electrons produced are accelerated and gain enough energy to perform further ionization. An avalanche develops and creates a signal. However, there is a serious drawback of such a geometry. The amplitude of the signal (that is proportional the total ionization) depends on the point where the interaction of the incident particle within the detector took place. Thus, the correlation between the energy of the incident particle and the measured signal is lost. This problem can be solved by choosing an geometry in which the avalange formation takes place only in close proximity to the wire. The most popular geometr is a cylindrical setup with a anode wire in the center. This geometry can be described by the two parameters a which is the wire diameter and b the distance between the wire surface and the detector wall, see Figure III.1 a). The lateral electric field decreases with  $r^{-1}$  as a function of distance from the wire (Figure III.1 b)). The exact expression is

**Figure III.1:** a) A slice of a proportional counter perpendicular to the signaling wire. b) The electric field as a function of distance r from the center of the counter. [Sauli77]

$$E(r) = \frac{CV_0}{2\pi\epsilon} \frac{1}{r},\tag{III.9}$$

which may also be written as a potential

$$\varphi(r) = -\frac{CV_0}{2\pi\epsilon} ln\left(\frac{r}{a}\right). \tag{III.10}$$

Here, r is the radial distance from the Wire,  $V_0$  the applied voltage,  $\epsilon$  the dielectric constant and

$$C = \frac{2\pi\epsilon}{\ln(\frac{b}{a})} \tag{III.11}$$

the capacitance per length. If an incident particle liberates one or more electrons somewhere within the counter, the electric field accelerates them towards the anode wire, but the electrons do not gather enough energy to cause further ionization.

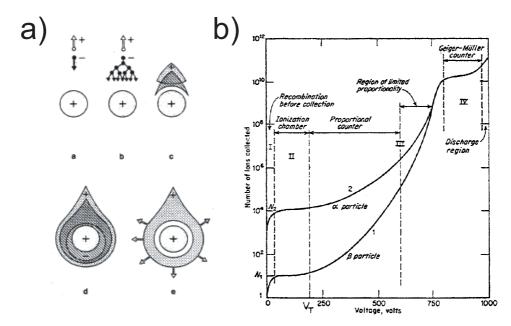

Only when they arrive at the very close proximity (a few radii in general) of the wire, the field strength is high enough to allow the creation of an electron avalanche. Because of lateral diffusion and the small dimensions the wire, the avalanche will completely surround the wire as shown in Figure III.2 a). If the number of electrons created in the avalanche is proportional to the number of electrons created in the primary ionization process, the signal is proportional to the energy of the incident particle. As shown in Figure III.2 b) this is only valid for a certain voltage range. If the device is operated within this range, it is called "proportional chamber". In this mode, gains from 10<sup>4</sup> up to 10<sup>6</sup> can be obtained. If the applied voltage is too low, the electrons will still be moved to the anode wire, but no amplification will occur. Therefore, the signal will be too low to be measured. If, on the other hand, the voltage is higher the proportionality is lost gradually, as space charges build up around the anode. Finally, at even higher voltages, avalanches will spread out over the whole counter and the signal will become completely independent of the primary electrons. This is called the "Geiger-Müller" region.

Figure III.2: a) Time development of an avalanche around an anode wire. b) The different modes of operation a proportional counter works depend strongly on the applied voltage. Here, the number of created ions is shown as a function of voltage. [Sauli77]

III.3 Gaseous detectors 27

#### Signal Creation and Readout

It is important to realize that the creation of the signal is due to the movement of charges within the electric field rather than to the collection of charges themselves. From electrostatics, the induced signal can be calculated. For a charge q that is moved dr within a detector of (total) capacitance lC the induced voltage dv is given by the equation

$$dv = \frac{q}{lCV_0} \frac{d\varphi}{dr} dr. (III.12)$$

In principle, the integration of this formula over the radius of the whole detector would lead to the induced voltage. However, as the electrons are liberated very close to the anode wire, their contribution to the signal is quite small. Assuming that all charges are created at the same distance  $d_C$  from the wire, the integral can be split up into two parts. Integration from a to  $d_C$  leads to the fraction of the signal created by the electrons  $(v^-)$  and from  $d_C$  to b that of the ions  $(v^+)$  respectively. The overall signal is of course given by

$$v = v^+ + v^-.$$

The ratio between the electron and the ion signal then is

$$\frac{v^{-}}{v^{+}} = \frac{\ln(a + d_{C}) - \ln a}{\ln b - \ln(a + d_{C})}.$$

(III.13)

For typical parameters (a=0.02 mm, b=10 mm,  $d_C=0.001$  mm), the ratio is  $\approx 0.8$  %. To obtain a formula for the time dependence of the signal is possible by assuming that all ions are leaving the wire region with constant mobility. Then, integration reads to

$$v(t) = -\int_0^t dv = -\frac{Q}{2\pi\epsilon_0 l} \ln \frac{r(t)}{a}.$$

(III.14)

Using the definition of mobility gives

$$\frac{dr}{dt} = \mu^{+} \frac{E}{P} = \frac{\mu^{+} C V_{0}}{2\pi \epsilon_{0} P} \frac{1}{t}.$$

(III.15)

Integrating this formula and substituting the result in III.14 finally leads to

$$v(t) = -\frac{Q}{4\pi\epsilon_0 l} \ln\left(1 + \frac{\mu^+ C V_0}{\pi\epsilon_0 P a^2} t\right) = -\frac{Q}{4\pi\epsilon_0 l} \ln\left(1 + \frac{t}{t_0}\right). \tag{III.16}$$

The total drift time can of course be obtained by the condition r(t) = b and is thus

$$T = \frac{\pi \epsilon_0 P(b^2 - a^2)}{\mu^+ CV_0}.$$

(III.17)

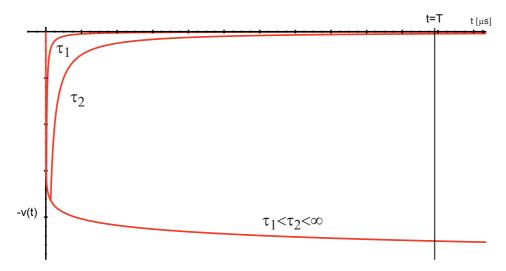

In Figure III.3 the function -v(t) combined with the exponential decharge for different time constants is shown. The function has a very steep rise at the beginning which means that most of the signal develops within about the first one thousands of the total time [Sauli77]. Therefore, the signal normally is differentiated by a RC-circuit<sup>5</sup> with time constant  $\tau = RC$ .

**Figure III.3:** Signals created by a MWPC. The sharp rise at the beginning is due to the drifting electrons. The later part is the exponential discharge of the chamber.

### III.3.3 Filling Gas

As the principle of avalanche multiplication does not depend on the type of gas, generally every gas or gas mixture can be used as filling gas. However, miscellaneous mixtures also differ very much in their properties. For example, some allow a very high gain factors while others guarantee good proportionality. As these requirements often conflict with each other, the choice of gas is always a compromise. Experimental results have shown, that in noble gases multiplication occurs at a much lower voltage than in more complex molecules. This is due to the fact that molecules with more than one atom have a number of non-ionizing dissipation modes (e.q. vibrational or translational states). Within the group of noble gases, argon is in most<sup>6</sup> cases the first choice for it is much less expensive than xenon or krypton.

In practice however, counters filled with argon only cannot exceed a gain of 10<sup>3</sup>

<sup>&</sup>lt;sup>5</sup>For details on RC-circuits see [Horowitz89]

<sup>&</sup>lt;sup>6</sup>The Alice TRD uses Xenon as it has a higher interaction probability for transition radiation.

to 10<sup>4</sup>. This is because of secondary ionization that takes place if an argon atom is excited but not ionized. The atom can return to its ground state only through the emission of a photon. The minimum energy of such a photon is 11.6 eV for argon and is thus well above the ionizion potential of a copper cathode, which is only 7.7 eV. Therefore, these photons can ionize the copper atoms and create further electrons that start new avalanches. Argon ions on the other hand migrate to the cathode where they are neutralized with an electron from the copper. The balance energy of this process is also either radiated or a secondary emission takes place [Sauli77]. These secondary electrons cause additional avalanches shortly after the initial one. This puts the counter in the regime of permanent discharge. To suppress these effects, another component is added to the gas mixture. As already mentioned, polyatomic molecules posses a number of non-ionizing absorption modes. Therefore, they can also absorb the photons created by the excited argon atoms without creating further electrons (methane, for example absorbs photons in a range from 7.9 up to 14.5 eV). This is a common property of most organic compounds but also of some inorganic molecules as  $CO_2$ ,  $BF_3$  or freon<sup>7</sup>. If an ionized polyatomic molecule neutralizes at the cathode, emission of a secondary electron is very unlikely. Instead, the molecule either dissociates or forms larger complexes (polymerisation). The second gas component is called "quencher", because it quenches the emitted photons and secondary electrons. Common mixtures are P10 which is 90% argon and 10% methan or a mixture of argon and CO<sub>2</sub>. Using a quencher with good photon absorption properties, gains larger than 10<sup>6</sup> are possible [Sauli77]. There are some more criteria for the choice of the gas, for a detailed discussion see [Sauli77].

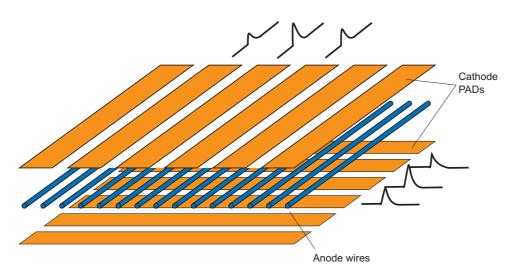

### III.4 Multi Wire Proportional Chambers

Even though proportional counters are well suited for the detection of the energy loss of radiation, a serious drawback is their lack of spatial resolution. It can only be determined whether a particle transversed a chamber or not. A straight forward approach to overcome this limitation would be a device with a multiwire structure. However, it was longtime believed that such a device would not work due to capaci-

<sup>&</sup>lt;sup>7</sup>Freon is a commercially available refrigerant. It is produced by the DuPont company. See http://refrigerants.dupont.com for details.

Figure III.4: Important geometry parameters of a typical MWPC. [Sauli77]

tive coupling between the individual wires. In 1967/1968, George Charpack<sup>8</sup> and his coworkers proved that black is white by constructing the first Multi Wire Proportional Chamber or MWPC short [Charpack68]. They recognized that the negative signals produced by capacitive coupling are largely compensated by the induced positive signals in all wires surrounding the anode of interest. In fact, every wire acts as a single, independent detector.

Soon after their invention, MWPCs became extremely popular in high energy physics. One reason is that until then, most detectors were optical in nature (e.g. cloud- or spark-chambers). There was a need for purely electronic devices to acquire data at higher rates and improve data processing. On the other hand, the developments in semiconductor electronics had just made it possible to handle large numbers of channels.

The basic geometry of MWPCs is almost everywhere the same<sup>9</sup>. The MWPC consists of a anode wire layer sandwiched between two cathode planes. Theses cathodes can either be wires as well or a continuous plane of some conductive material. In most cases, this material is subdivided into so-called "pads". This allows a special readout technique that will be explained in the following. In Figure III.4, the geometry and common names of important geometrical parameters are shown. Because the electric field within the chamber is very sensitive to the position of the wires, they are kept under mechanical tension to assure that they stay in their positions. This requires a very stable frame which is one of the main mechanical defiances in the construction of MWPCs. If the chamber's dimensions exceed a certain limit (about 1 m), there even have to be supportive elements for the wires.

<sup>&</sup>lt;sup>8</sup>Georges Charpak is a Polish-French physicist. We was born on August 1, 1924. In 1992, he obtained the Nobel price in physics "for his invention and development of particle detectors, in particular the multiwire proportional chamber"

<sup>&</sup>lt;sup>9</sup>One common extension are driftchambers, for details see [Blum93] or cylindric chambers.

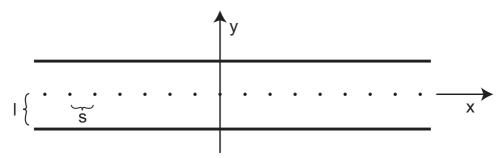

#### III.4.1 Electrostatics within a MWPC

The electric field or the electric potential respectively can be obtained by solving Laplace's  $^{10}$  equation

$$\Delta V(x, y, z) = 0 \tag{III.18}$$

with appropriate boundary conditions. Assuming an infinite wire plane and a zero wire diameter, the problem is invariant under any translation in z and only the two dimensional Laplace equation for a potential V(x,y) has to be solved. As to be expected, the field is constant and the field lines are parallel to each other and orthogonal to the cathode planes in most of the chamber. They are similar to the field lines in a plate capacitor with the same dimensions. However, in proximity to the wires, the field is deformed as shown in Figure III.5 a). Even though an analytical formula for the potential can be obtained [Blum93], today simulations are the appropriate tool to get detailed information on the electric field. These are based on numerical solutions of the Laplace equation. In the simplest case, a cartesian grid is placed over the whole chamber. The differential operator  $\Delta$  is then replaced by finite differences on the grid. A simple forward Euler<sup>11</sup> algorithm

$$V(i,j) = \frac{1}{4} \left[ V(i+1,j) + V(i-1,j) + V(i,j+1) + V(i,j-1) \right]$$

(III.19)

already produces some results. In this equation  $V(i,j) = V(x+i\Delta x, y+j\Delta y)$  if  $\Delta x$  and  $\Delta y$  are the cell sizes of the cartesian grid. However, more sophisticated (i.e. finite element) methods provides a convergence of higher order. For details see [Burger06] or [Giordino97].

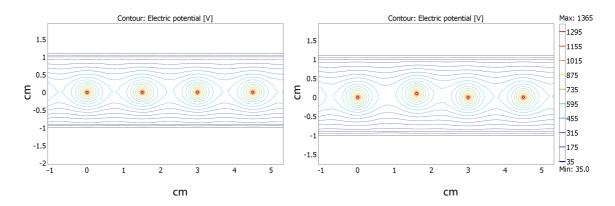

Furthermore, simulations can give information of field disturbance if for example one wire is slightly displaced. This is shown in Figure III.5 b)

### III.4.2 Readout and Resolution Recovery

In principle, there are several possibilities to readout a MWPC. The simplest would be to consider each wire to be a single detector with its own electronics. This approach has several drawbacks. It results in a large number of channels to be read (a chamber with a 20 cm wire plane, a wire radius of 20  $\mu$ m and a wire distance of

<sup>&</sup>lt;sup>10</sup>Pierre-Simon Laplace was french mathematician. He was born in March 23, 1749 in Beaumont-en-Auge (Normandie) and died March 5, 1827 in Paris.

<sup>&</sup>lt;sup>11</sup>Leonhard Paul Euler was a swiss mathematician. He was born April 15 1707in Basel and died September 18 1783 in St. Petersburg.

Figure III.5: a) Equipotential lines for a chamber with 20  $\mu$ m wire diameter, 1.5 mm distance between the wires and 1 mm between wire- and pad-plane. b) Equipotential lines for the same geometry. One wire is displaced by 10 % in x- and y-direction. All plots have been created with COMSOL using a finite element method.

Figure III.6: Schematic setup of a MWPC with pad readout. [Sauli77]

1.5 mm contains  $\approx 130 \text{ wires}$ ), every wire must be soldered to a single output pad and has to be decoupled from the high voltage. Although this is possible with modern electronics, it would provide spacial resolution only perpendicular to the direction of the wires, i.e. in one dimension. To overcome these limitations, the cathode plaines are subdivided into so-called "pads". These are strips that are electrical insulated from each other. Therefore the charge induced by the moving ions is shared by a number of pads and can be measured as a function of pad number. Using the center

of gravity method (i.e. weighted average) of several pads gives a first estimate for the coordinate of the incident particle. The avalanche on the anode wire is also highly localized along the wire direction [Leo87]. This allows, using two perpendicular pad planes, to determine both x and y coordinate. A setup of such a MWPC is shown in Figure III.6.

To understand how the signal on the pads is created, we consider a setup in which only one of the two cathode plaines has one pad which means that it is split up into three pieces. Furthermore, we assume a series of avalanches that come from a straight particle track and neglect the width of the avalanches. The track is then reduced to a infinite thin line of charge with density  $\lambda$ , located in the middle of a capacitor. The goal is to calculate the surface charge density  $\sigma(x)$  induced on the pad. From Gauß<sup>12</sup> law

$$\sigma(x) = \epsilon_0 E(x) \tag{III.20}$$

holds. To obtain an expression for the electric field E, we use the Method of  $images^{13}$ . The images of a line of positive charge are alternating positive and negative lines at the position

$$z_k = \pm (2k+1)\frac{D}{2}, \qquad k = 1, 2, \dots \text{ and } z_0 = -\frac{D}{2}.$$

(III.21)

Each pair of these lines at  $\pm z_k$  creates an electric field which is normal to the surface at z=0 and is equal to

$$E_k^{(n)} = \frac{\lambda}{\pi \epsilon_0} \frac{z_k}{x^2 + z_k^2}.$$

(III.22)

As the total surface charge is the sum of all these parts, this leads to

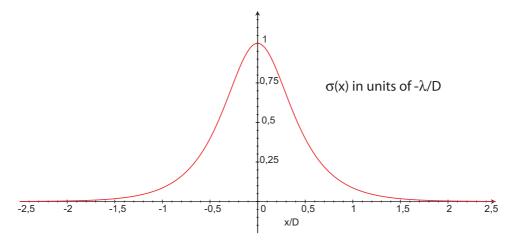

$$\sigma(x) = -\frac{\lambda}{\pi} \sum_{k=0}^{\infty} (-1)^k \frac{(2k+1)\frac{D}{2}}{x^2 + (2k+1)^2 \frac{D^2}{4}} = -\frac{\lambda}{2D} \frac{1}{\cos\left(\frac{\pi x}{D}\right)}.$$

(III.23)

This function is shown in Figure III.7. Note that the integral

$$\int_{-\infty}^{\infty} \sigma(x)dx \tag{III.24}$$

is  $-\lambda/2$ . This means that half of the original charge is transferred to a cathode plain of infinite dimension.

<sup>&</sup>lt;sup>12</sup>Johann Carl Friedrich Gauß was born on 30 April 1777 in Braunschweig and died 23 February 1855 in Göttingen. He was a german mathematician and scientist and contributed to many field, e.g. number theory, magnetism, etc.

<sup>&</sup>lt;sup>13</sup>The principle of this method is explained in [Nolting07] or every other book on electrostatics.

**Figure III.7:** Charge density induced on a pad by a line of charge with density  $\lambda$  [Blum93].

#### Spacial Resolution and PAD Response Function

To reconstruct the coordinate of an incident track from the signals measured on the pads, the amount of charge deposited on a pad as a function of the coordinate of the incident particle is needed. If W is the width of a pad strip, and x the distance from the center of the strip, this is given by

$$P(x) = \int_{x - \frac{W}{2}}^{x + \frac{W}{2}} \sigma(x') dx'.$$

(III.25)

P(x) is called "pad response function". The important fact for reconstruction of the coordinate is, that this function can be approximated by a Gaussian curve,

$$P_0(x) \approx Ae^{-\frac{x^2}{2s_0^2}}.$$

(III.26)

This was determined experimentally [Blum93]. Measuring the signals on three consecutive pads results in the system of equations

$$p_{i-1} = A \exp\left(-(x - (x_i - W))^2 / 2s^2\right)$$

(III.27)

$$p_i = A \exp\left(-(x - x_i)^2 / 2s^2\right)$$

(III.28)

$$p_{i+1} = A \exp\left(-(x - (x_i + W))^2 / 2s^2\right),$$

(III.29)

with  $p_i$  the pulse height on the *i*th pad and  $x_i - W$ ,  $x_i$ ,  $x_i + W$  the centers of three adjacent strips. A is a constant proportional to the overall charge. In principle, the three unknowns A, x and s can be obtained by solving this system if  $p_i$ ,  $p_{i-1}$  and  $p_{i+1}$  are measured. However, solving it for s first,

$$s^{2} = -W^{2} \ln \left( \frac{p_{i-1}p_{i+1}}{p_{i}^{2}} \right), \tag{III.30}$$

makes it possible to measure the pad response function and thus determining s in advance. The coordinate x is then given by  $^{14}$

$$x = \frac{1}{w_1 + w_2} \left[ w_1 \left( x_i - \frac{W}{2} + \frac{s^2}{W} \ln \frac{p_i}{p_{i-1}} \right) + w_2 \left( x_i + \frac{W}{2} + \frac{s^2}{W} \ln \frac{p_{i+1}}{p_i} \right) \right].$$

(III.31)

The weights  $w_1$  and  $w_2$  are usually chosen as  $p_{i-1}^2$  and  $p_{i+1}^2$  as the measurement error is roughly proportional to the recorded pulse height on the strips with the smaller heights, cf. [Blum93].

# III.5 The Münster Prototype

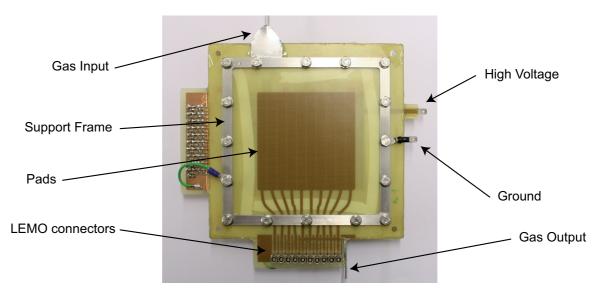

Figure III.8: Photo of the 3 mm wire-to-pad prototype with 10 pad strips.

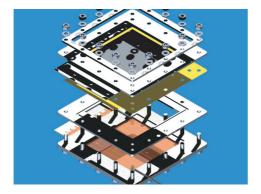

With the goal of building a complete small animal PET prototype, the construction of MWPC prototypes for this purpose started in Münster in 2005. As mentioned above, the idea of a wire chamber based small animal PET has already been realized in the quadHIDAC scanner. However, as these devices (and service quantities) are no longer commercially available, it was decided to start the design of msPET. The first step was the design of small MWPCs needed for this purpose. The prototype consists mostly of F10 (or G10 which is the halogen free version of F10). This is a compound of woven glass and epoxy as usually used for printed circuit boards

<sup>&</sup>lt;sup>14</sup>This equation is easily calculated by combining eqn. XX a) and XX b) first, then XX b) and XX c) and finally add these two terms for x with the weights  $w_1$  and  $w_2$ .

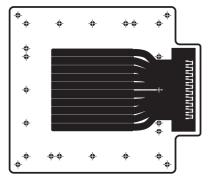

(PCBs). Therefore, it is commercially available with a laminated copper layer. It has been chosen because of it good insulation properties, does not outgase and has a small radiation length. Furthermore, it provides enough mechanical stability to act as a frame for wires under tension. As shown in Figure III.9 a), the chamber is composed of four layers: a frame supporting the wires sandwiched between two pad planes. The pads are made of copper. They are etched using a negative pattern (Figure III.9, b), exactly as done for regular PCBs. At the end of the plane, every pad is connected to a LEMO connector. Two stainless steel pipes on two opposite sides allow a continuous flow of the gas mixture. To apply high voltage to the wires, they are all soldered onto a strip of copper that is connected to an external pin. For additional stability, two stainless steel frames are screwed together with the whole chamber.

The initial prototype had a wire-to-pad distance of 3 mm and a gas volume of  $100 \times 100 \times 3$  mm<sup>3</sup>. However, measurements with lead foils showed that electrons created within these foils by  $\gamma$  photons leave them under a certain angular distribution with mean exit angle

$$\alpha_{mean} = 36.0^{\circ} \pm 2.8^{\circ}$$

[Hünteler07]. This has a negative effect of the spacial resolution of the chamber that scales with the height of the chamber. To preserve its good intrinsic resolution, a thiner prototype (1 mm wire-to-pad distance) has been built. For further details, see [Hünteler07].

In addition, two versions of the 1 mm prototype with different pad sizes were built. In the first version, the pads have a width of 9.7 mm. In the second version, the width has been reduced to 3.03 mm to optain a higher spatial resolution.

**Figure III.9:** a) Engineering plans of the first MünsterPET prototype. b) The negative used to etch the pads. [Gottschlag07]

# CHAPTER IV

# Experimental Evaluation of the msPET MWPC Prototypes

Before building a complete small animal PET prototype, it is important to assure that the MWPC prototypes work properly. Therefore, a number of tests have been performed. Beginning with simple event maps it has been tried to examine the efficiency and spatial resolution of the prototypes.

# IV.1 Event Maps

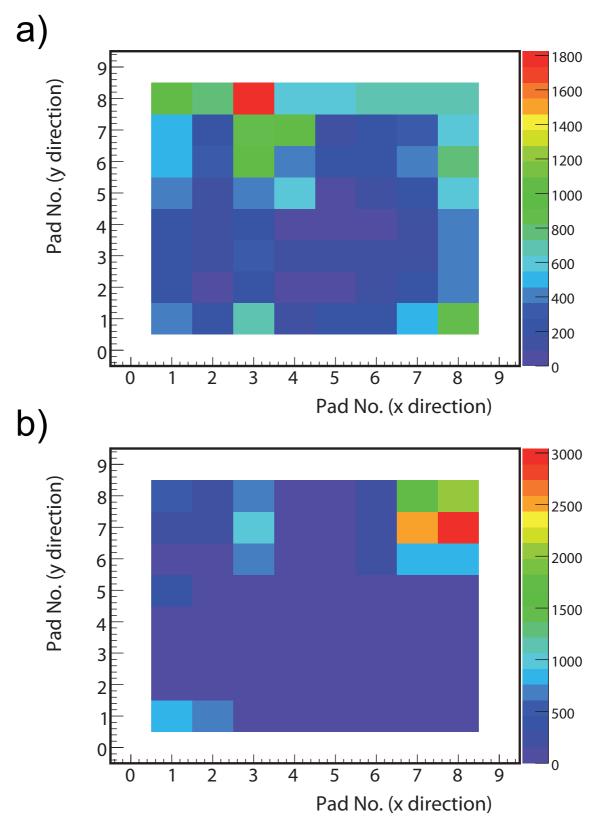

Here, the term event map refers to a plot in which a histogram is filled with the number of the pad carrying the highest charge in each single event. Combining the information of the two perpendicular pad planes, the result is a checker board like pattern.

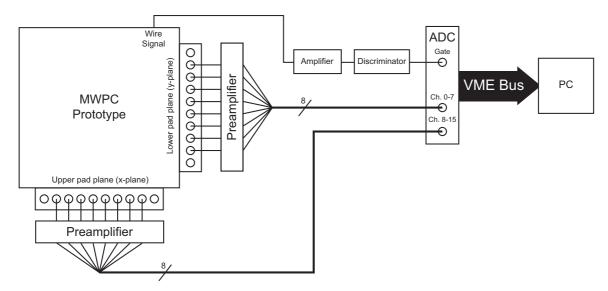

To create such maps, it is necessary to be able to read the voltages on all pads. For the first 1 mm prototype, this means 20 values. However, as the peak sensing ADCs<sup>1</sup> used feature only 16 channels per module, only the eight inner pads per plane have been considered. As the ADCs need a gate, the signal from the wires plane of the MWPC has been used as a trigger. This setup in schematically shown in Figure IV.1. The first test that has been done was the measurement of cosmic radiation. As

Figure IV.1: Setup for acquiring event maps.

this radiation is equally distributed over the surface of the whole chamber, the event map should, neglecting statistical variations, essentially be homogeneous. However, as shown in Figure IV.2 a) this is not the case. There are fluctuations, especially

$<sup>^{1}\</sup>mathrm{ADC}$  stands for analog digital converter.

IV.1 Event Maps 39

**Figure IV.2:** a) Shows a event map created using cosmic radiation as source. 25,000 events were taken. b) Event map created with a  $^{55}Fe$  source positioned on the top right corner of the chamber. 25,000 events were taken.

at the border of the map. There is a number of possible explanations for this. For example, different wire tensions could lead to a deformation of the electric field within the chamber and thus a different gain in different regions (cf. Figure III.5). Furthermore the area of increased activity coincidences with the gas inlet. Due to perturbations, a higher density of the gas could arise. This also would lead to more events.

In the next step a X-ray source has been placed on the chamber. A <sup>55</sup>Fe source with an activity of 37 MBq has been used. It emittes photons at a energy of 231 keV in electron capture. In Figure IV.2 b), a event map with the source placed on the chamber is shown.

These event map suggests that the chamber is working as desired because the position of the source on the chamber can be seen in the plot. However, more detailed measurements were performed to study the chamber in more detail and determine the important parameters efficiency and spatial resolution.

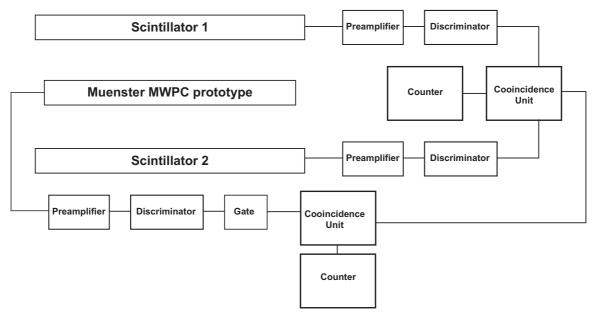

### IV.2 Efficiency

Figure IV.3: Schematical view of the efficiency setup.

Efficiency is defined as the number of charged particles that are detected by the chamber over the total number of particles traversing it. To test the prototype, cosmic rays were used as source. In the lower atmosphere, they consist mostly of muons

IV.2 Efficiency 41

and electrons. The flux of the myons crossing a unit horizontal area is  $\approx 130~\rm m^{-2}s^{-1}$  or  $\approx 50~\rm m^{-2}s^{-1}$  for electrons respectively. The mean energy of the myons is about 4 GeV [PDG06]. For Argon, the number of primary ions created by minimum ionizing particles is 22.9 per cm [Kleinknecht84] and thus 2.3 per mm. As in principle, every electron released in the gas starts an avalanche, theoretically an efficiency of 100% is expected and values up to 95% have been obtained for other chambers, see [Nettebrock91].

To experimentally determine the efficiency, the chamber has been "sandwiched" between two scintillators, operating in coincidence. This is necessary to consider only particles that really cross the chamber. Furthermore, it reduces the noise of the photomultipliers. Assuming that they are able to detect every charged particle that transverses them, the efficiency of the chamber is simply the number of coincidences of the photomultipliers and the chamber over the number of photomultiplier coincidences only. The complete setup is schematically shown in Figure IV.3.

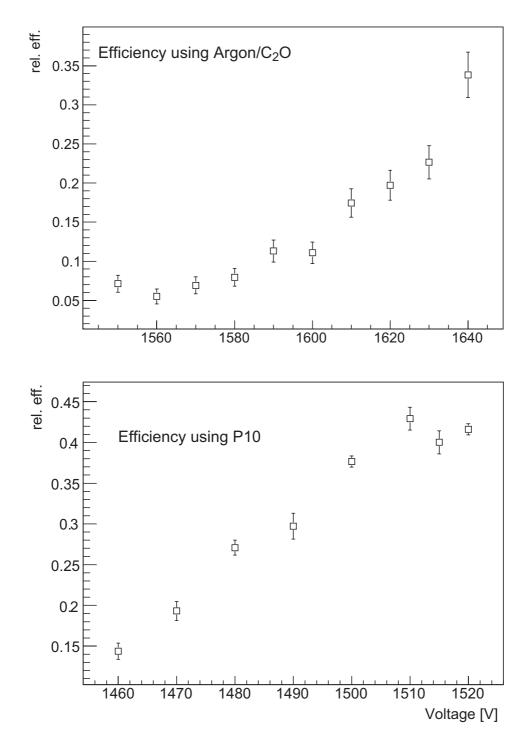

Efficiency measurements have been done for both P10 and a 82% Argon/18% CO<sub>2</sub> mixture using the 1 mm prototype. The results are shown in Figures IV.4. For P10, above 1520 Volt the chamber got into a mode of spontaneous discharge and could no longer be operated. Using the Argon/CO<sub>2</sub>, the chamber could be operated up to 1640 Volt due to the better quenching properties of this mixture. As the rate of events became very low for the Argon/CO<sub>2</sub> mixture at lower voltages, the measurement was started at 1540 Volt. The measurements show that the chamber achives a maximum efficiency of about 40% at 1520 Volt using P10 and of about 35% at 1640 Volt using Argon/CO<sub>2</sub>. There are two possible explanations for these results. Either, the chamber has to be operated at a higher voltage and thus at a higher electrical field. This would allow the chamber to create a measurable signal even when only very few electrons are created. The other possible explanation is that for a chamber with such a small gas volume, the number of electrons created is not always high enough to start an avalanche.

Furthermore, it would be worthwhile to repeat the measurements with other gas mixtures. In fact, a system allowing the flexible mixing of Argon with CO<sub>2</sub> or other quenching gases is currently beeing installed in Münster.

**Figure IV.4:** Results for the efficiency measurements. a) Using P10 as a filling gas b) Using Argon/CO<sub>2</sub> as a filling gas. Both measurements were taken using a 1 mm prototype.

# IV.3 Gas Gain and Pulse Heights

As derived in a previous chapter (Equation III.8), the gas gain of a MWPC is defined as

$$M = \frac{n}{n_0} = e^{\alpha x}.$$

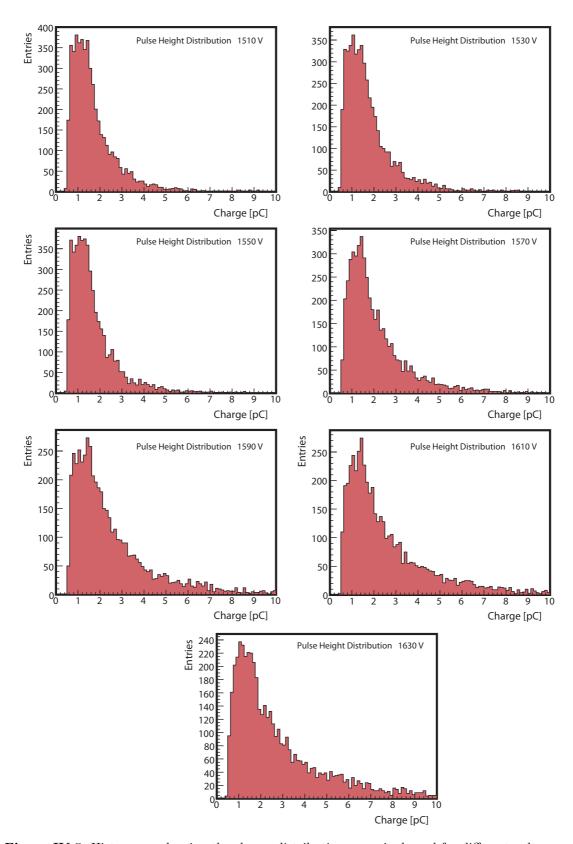

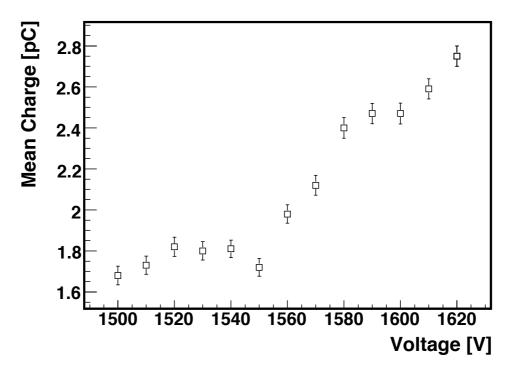

Furthermore, it has been shown that the amount of charge deposited on a pad is proportional to the number of secondary electrons n. This means that using a charge sensitive preamplifier, it is possible to determine M from the height of the measured signal. Here a Ortec Model 124 amplifier with a gain of 275 mV/pC has been used. The output of the amplifier has been further analysed with a LabView<sup>2</sup> based readout system. This system is able to automatically determine the pulse height. Finally, a histogram of the pulse height distribution of 5000 pulses at a given voltage was created. This has been done a range from 1500 to 1620 volts, in steps of 10 volts. Figure IV.5 shows every second histogram. As it is not clear, how many electrons are created in the primary process (most likely the interaction of a myon with the gas volume), only the measured charge is shown. Note that using only one pad, it has to be assumed that in most cases only a fraction of the charge induced is really measured. This is due to the fact that the charge is normally distributed to two or three adjacent pads. However, according to theory, a shift of the mean of the histogram is expected as the gain should increase with the voltage. The mean value versus the voltage is shown in Figure IV.6. The plot confirms the increase of the mean charge as a function of voltage.

#### IV.3.1 Simulations with Garfield

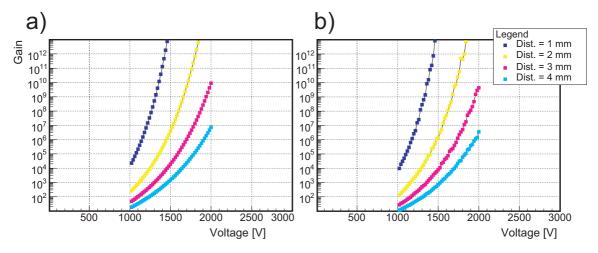

The measurements have also been compared to simulation made with Garfield. Garfield is a program dedicated to the simulation of MWPCs. It has been developed in 1984 by Rob Veenhof at CERN<sup>3</sup>. Garfield allows the simulation of the electric potential within the MWPC as well as the gain factor. For the msPET geometry, the gain has been simulated using a standard numerical method as well as a Monte Carlo simulation. This has been done for different gas mixtures. The results are displayed in Figure IV.7. Unfortunately, the gain predicted by Garfield is much higher than the measured one. Above a certain voltage, the predicted values become as

<sup>&</sup>lt;sup>2</sup>LabView is a graphical data acquisition system. For details see [Baumann05, Gottschlag05].

<sup>&</sup>lt;sup>3</sup>CERN stands for European Organization for Nuclear Research.

Figure IV.5: Histograms showing the charge distribution on a single pad for different voltages.

Figure IV.6: The Mean Charge is increasing as a function of voltage.

high as  $10^{19}$  and stay constant. This most likely means that the algorithm used in Garfield does no longer works properly for the given set parameters.

### IV.4 Spatial Resolution

Spatial resolution is the ability of the MWPC to resolve the position where it has been traversed by a charged particle. It is usually defined as the minimum distance at which two events can still be separated. To determine the spatial resolution of our prototype, we used the <sup>55</sup>Fe source partly collimated by a mask. The mask consists of pairs of holes with different distances between them as shown in Figure IV.8. To reconstruct the position of the incident particle from the signal measured on the pads, the pad response method that is described in III.4.2 has been used. Here, the approach to approximate the PRF with a exponential function

$$P_0(x) \approx e^{-\frac{x^2}{2s^2}}$$

**Figure IV.7:** Simulated gains for a) P10 and b) 82% Argon/18% CO<sub>2</sub> mixture for different pad to wire distances.

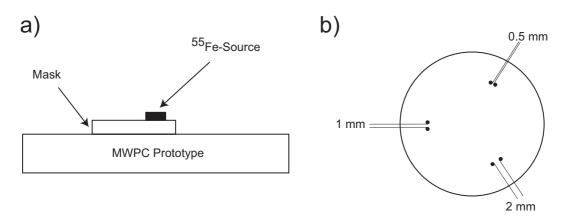

**Figure IV.8:** a) Determining the spatial resolution using a discriminator mask and a <sup>55</sup>Fe source. b) Detailed view of the discriminator mask.

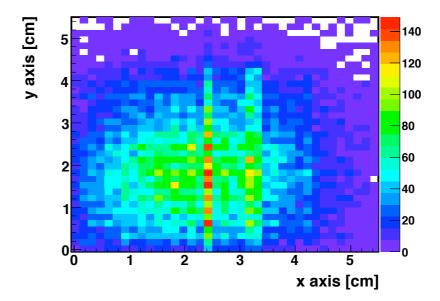

**Figure IV.9:** Reconstructed image using the pad response function of a <sup>55</sup>Fe source collimated by two wholes with a diameter of 1 mm each. The distance between the center of the holes is 2 mm. It is not possible to distinguish between the contribution of the two holes. The lines in the middle is regarded as some measurement artefact.

has been used. Thus, the first step in this method is to determine the parameter s. This has been done as described in III.4.2, using a cosmic ray data set with 120,000 events. The results are (for a pad width of W=0.3 cm)

$$s_x = 0.33 \text{ cm}$$

$s_y = 0.30 \text{ cm}$  (IV.1)

for the x- or y-plane respectively. The error of these quantities is due to the measured signals on the pads and thus depends on the gain of the preamplifiers and on the accuracy of the ADCs. As it is very hard if not impossible to obtain quantitative results for these errors, the overall error of  $s_x$  and  $s_y$  are neglected here. However it is clear that this error has a negative effect on the spatial resolution. In the next step, a measurement with the  $^{55}$ Fe source discriminated by two holes with distance 2 mm and 55,000 events has been reconstructed. The result is shown in Figure IV.9. The lines in the middle of the plot is regarded as an error of the data acquisition system. However, neglecting this, it is still not possible to determine the position of the two holes in the collimation mask. Thus, the spatial resolution of the msPET prototype could not be determined.

# CHAPTER V

# The n-XYTER Readout Chip

n-XYTER stands for neutron-X-Y-Time-Energy Read-out. The n-XYTER is an ASIC¹ readout chip which has been developed within the framework of the european project DETNI. Although it has been intended to use for the detection of neutrons, its specifications perfectly match the needs of a readout chip for multi wire proportional chambers. This is because neutrons as well as gamma rays emitted by electron positron annihilation are statistical in nature. All 128 channels on the chip are purely data driven and therefore no external trigger is needed. Containing an integrated timestamp generator with a resolution up to 1 ns [Brogna06] the detection of coincidences in PET is easy to realize.

Still, as there is no readout board available at the moment, a prototype of such a board has been developed based on the DL701 LogicBox created in Heidelberg. This box contains a Xilinx Spartan 3 FPGA<sup>2</sup> which is able to process the n-XYTER's data and perform slow control via I<sup>2</sup>C<sup>3</sup> as well as a USB interface to communicate with any standard PC. To convert the analog peak height output signal of the n-XYTER, a MAX106 flash ADC<sup>4</sup> has been used.

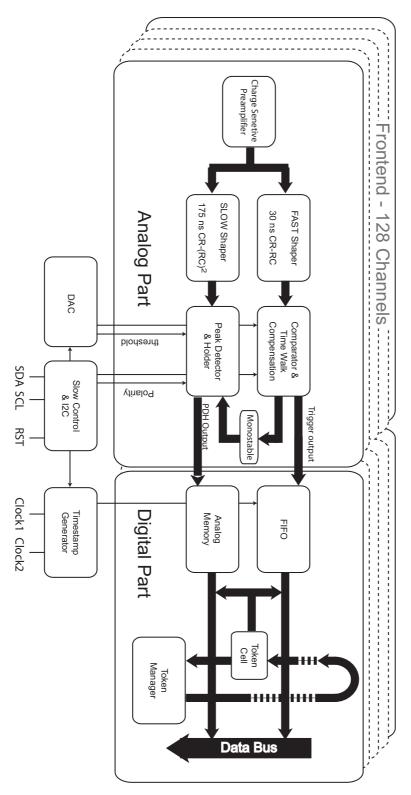

### V.1 Internal Layout of the n-XYTER

The n-XYTER consists of an analog front-end part that performs pulse height detection and time stamp creation. It is followed by a clock synchronous back end that is responsible for the derandomization of the recorded data. The complete analog part as well as some fraction of the back end are repeated for every of the 128 channels. Furthermore, the n-XYTER contains several units for slow control via I<sup>2</sup>C, digital to analog converters (DACs) to set trigger thresholds as well as a clock driven timestamp generator and a token manager. An overview the n-XYTER's architecture is given in Figure V.1.

The n-XYTER can be driven by two independent clocks, clk256A and clk256B. They are applied via different input pads. clk256A is the main clock for the chip. It drives the counter which creates the first 12 MSBs<sup>5</sup> of the timestamp (MSB first) and is used for the synchronisation of test signals. By default, it also generates the readout-clocks clk32o and clk128o. The secondary clock, clk256B can be used for

<sup>&</sup>lt;sup>1</sup>ASIC stands for Application Specific Integrated Circuit.

<sup>&</sup>lt;sup>2</sup>FPGA stands for Field Programmable Gate Array

<sup>&</sup>lt;sup>3</sup>I<sup>2</sup>C stands for Inter Integrated Circuit Bus

<sup>&</sup>lt;sup>4</sup>ADC stands for **A**nalog **D**igital **C**converter.

$<sup>^5 \</sup>mathrm{MSB}$  stands for  $\mathbf{M}\mathrm{ost}$  Significant  $\mathbf{B}\mathrm{it}$

Figure V.1: The n-XYTER's chip architecture [Brogna07].

readout clock generation as well. Furthermore, it can be used to generate the LSB<sup>6</sup> of the timestamp. Originally, clk256B has been indended as a failback for the first design. In case clk256A failed, it could take over its function [Schmidt07].

### V.1.1 Analog Frontend

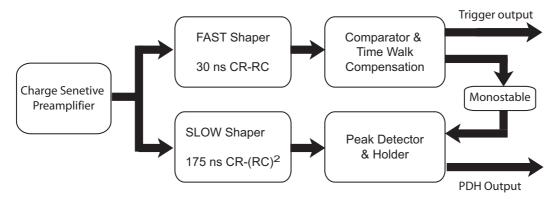

The layout of the analog front-end is shown in Figure V.2. As each channel features its own analog front-end, this circuit is present 128 times within the chip. The front-end begins with a charge sensitive preamplifier which is based on a classical folded-CASCADE architecture [Brogna06]. To keep noise low, a n-tpye MOSFET is used. Finally, the signal is differentiated (by a Cr-Rd passive network) within the preamplifier.

In the next step, the signal is split up into two parts. One is fed into the fast-the other one into the slow-shaper. Within the fast-shaper, a fast uni-polar pulse is generated by a 30 ns peaking-time shaper. This shaper is followed by a comparator and a time-walk compensation circuit. The comparator compares the signal to a fixed value generated by DACs<sup>7</sup> and thus acts as a trigger for the signal. The time-walk compensation is needed to obtain an amplitude independent timestamp. The second part of the signal is processed in the slow-shaper, which has a peaking time of 175 ns. The pulse is then transferred to a peak detector and holder circuit to determine the pulse height.

As the n-XYTER allows direct access to the fast- and slow-shaper outputs of the test channel via external pads, these signals can be visualized with an oscilloscope.

Figure V.2: The Analog Front-End Part of the n-XYTER.

$<sup>^6</sup> LSB$  stands for Least Significant Bit

<sup>&</sup>lt;sup>7</sup>DAC stands for **D**igital **A**nalog **C**onverter

### V.1.2 Digital Part

Following the analog front-end, the output of the fast shaper is used to generate a timestamp. This is done using a 12 bit counter, called timestamp generator, driven by clk256A. In addition clk256B can be used to create the LSB of the timestamp (according to register settings). The timestamp is then stored in a FIFO<sup>8</sup> memory, triggered by the fast-shaper signal via a SR latch. Meanwhile, the slow signal, i.e. the output of the peak detection and holder circuit is stored within an analog memory<sup>9</sup>. The further processing is organised as a token ring readout. This means, a token manager generates a so-called token, which asynchronously passes from channel to channel. The token is generated only if at least one of the FIFOs has data in it. The output of the FIFO and the analog memory for each channel are controlled by a token cell. If there is data available on a channel when the token arrives, the data readout is initiated and the stored analog and digital values are transferred to the data bus. In the next readout clock cycle, the token continues to the next channel containing data and finally returns to the token manager. At the end of the data bus, the digital data is demultiplexed and converted to the LVDS<sup>10</sup> signaling standard. The analog signal is also converted to a differential standard. Finally, these signals are set on the output pads.

#### V.1.3 Slow Control and Test Channel

To control the overall behaviour of the n-XYTER (e.g. DAC settings, mask channels, etc.) the chip possesses 45 registers, which can all be addressed via I<sup>2</sup>C. The first 16 registers (i.e. register 0 to 15) are used to mask every of the 128 input channels. Registers 16 to 31 set up the front-end DAC values used by the comparator circuit. Register Vth (18) is of special interest. Vth sets the comparator threshold voltage thus defining the trigger threshold for the input channels. Registers 32 and 33 are actual configuration registers and will be treated in more detail in the following. There are also some status registers that contain information of the missing token counter (register 36 to 37) and the overflow counter (34 to 35). Theses registers are read-only and automatically reset after each readout. Moreover, there are some

<sup>&</sup>lt;sup>8</sup>FIFO stands for **F**irst **In F**irst **O**ut. This means that the element first stored in the memory is also the first to appear on the output, like in a queue. The opposite principle is called LIFO meaning Last in First Out.

<sup>&</sup>lt;sup>9</sup>An analog memory is basically made of a capacitors and switches. For details, see [Leo87]

<sup>&</sup>lt;sup>10</sup>LVDS stands for Low Voltage Differential Signaling.

registers to control the clock (43 to 45), the test pulse (38) and the test trigger delay (39) as well as one register (42) to trim the DAC. Table V.1 gives an overview of all registers.

The n-XYTER provides several test features for the analog and digital part. In

**Table V.1:** The n-XYTERs I<sup>2</sup>C registers. [Brogna07]

| I <sup>2</sup> C Address | Register                                                 |  |  |

|--------------------------|----------------------------------------------------------|--|--|

| 0 - 15                   | mask registers (external)                                |  |  |

| 16 -31                   | reserved for front-end DACs (external)                   |  |  |

| 32 - 33                  | configuration register                                   |  |  |

| 34 - 35                  | overflow counter, readout only, reset after readout      |  |  |

| 36 - 37                  | missing token counter, readout only, reset after readout |  |  |

| 38                       | test pulse delay register                                |  |  |

| 39                       | test trigger delay register                              |  |  |

| 40 - 41                  | Spare                                                    |  |  |

| 42                       | trim DAC register (bit 0-4)                              |  |  |

| 43                       | clock delay register No. 1                               |  |  |

| 44                       | clock delay register No. 2                               |  |  |

| 45                       | clock delay register No. 3                               |  |  |

test mode 0 (full test mode), a pulse is generated within the calibration block and submitted to the analog channels via a 100 pF capacitor. The pulse is applied to groups of every 4th channel, according to the settings in register 32. However, in a chosen group, it still can be decided if the test pulse is applied to a single channel using the mask register. The pulse height - and thus the amount of injected charge - is set in a register called 'cal' (24). Furthermore, the polarity of the test pulse can also be set in register 32.

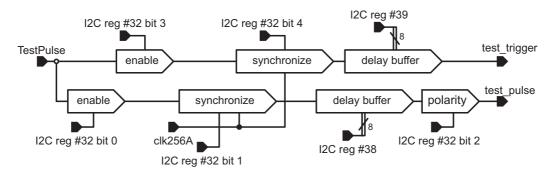

In test mode 1, a test trigger is transferred directly to the digital part of the n-XYTER allowing to test the timestamp generation. The test trigger has to be applied externally as shown in Figure V.3. Furthermore, the test pulse and test trigger signals can be delayed if needed.

**Figure V.3:** The creation of the test\_pulse and test\_trigger signals from the TestPulse input pad [Brogna07].

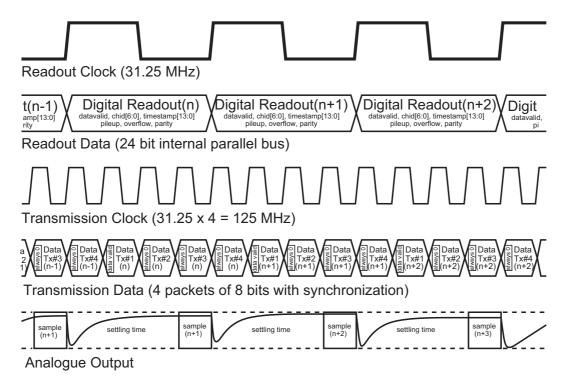

# V.2 The n-XYTER's Digital Data Output Format

The n-XYTER generates two readout clocks either from clk256A or clk256B (according to the settings of bit 3 in I<sup>2</sup>C-register No. 33). They are called clk32o and clk128o. These clocks are generated by dividing the chips main clock. If the chip is operated at the standard frequency of 256 Mhz, they are running at 32 Mhz (clk32o) or 128 Mhz (clk128o). Each pulse recorded is encoded in a 25 bit package (see Figure

**Table V.2:** n-XYTER digital data output. The four packages of 8 bits are transmitted consequitively. dv means data-valid. [Brogna07]

|   |   | 7  | 6   | 5   | 4   | 3   | 2      | 1     | 0      |

|---|---|----|-----|-----|-----|-----|--------|-------|--------|

| ( | ) | DV |     |     |     |     | TS9    |       |        |

| ] | 1 | 0  | TS6 | TS5 | TS4 | TS3 | TS2    | TS1   | TS0    |

| 4 | 2 | 0  | ID6 | ID5 | ID4 | ID3 | ID2    | ID1   | ID0    |

| ę | 3 | 0  | 0   | 0   | 0   | 0   | PileUp | OverF | Parity |

V.2). The timestamp is 14 bits, the channel id 7 bits wide. The package also contains a data-valid bit, as well as a pile-up, an overflow and a parity bit. These 25 bits are split up into 4 packages of 8 bit width which are transmitted on consecutive cycles of *clk1280*. Furthermore, they are transmitted in gray code<sup>11</sup>. The analog pulse

<sup>&</sup>lt;sup>11</sup>Gray code is an alternative binary decoding scheme for numbers. In gray code, two successive values differ by only one bit. This is especially useful for error correction.

height information is provided on the output simultaneous to the transmission of the 3rd data package. The detailed timing can be seen in Figure V.4. The packages are transmitted synchronous to *clk128o*. *clk32o* is used to determine the start of a each package (V.2).

However, actual measurements at the GSI<sup>12</sup> have shown that *clk1280* is shifted by 180 degrees with respect to the Figure V.4 [Lalik07]. This is important to assure proper timing when merging digital and analog data.

**Figure V.4:** Data scheme of the n-XYTER's digital output. Readout clock refers to *clk32o*, transmission clock to *clk128o* [Brogna07].

$<sup>^{12}\</sup>mathrm{GSI}$  stands for **G**esellschaft für **S**chwer**i**onenphysik and is located near Darmstadt.

# CHAPTER VI

# A Readout Board Prototype

# VI.1 Field Programmable Gate Arrays

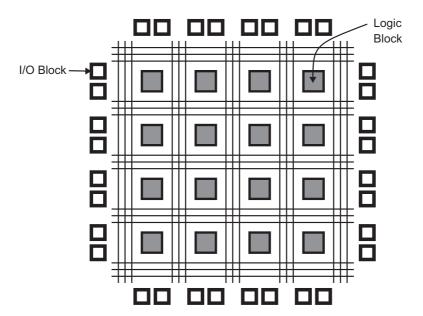

Field Programmable Gate Arrays are user programmable devices that allow the implementation of complex logic functions. They are able to process multiple signals at a time and are thus often used for data processing at high rates [Maxfield03]. This makes them an ideal core for a dedicated n-XYTER readout board. In the following sections, their historical development, architecture as well as the design process will be described. Special attention is payed to the Xilinx Spartan 3 device that is used here.

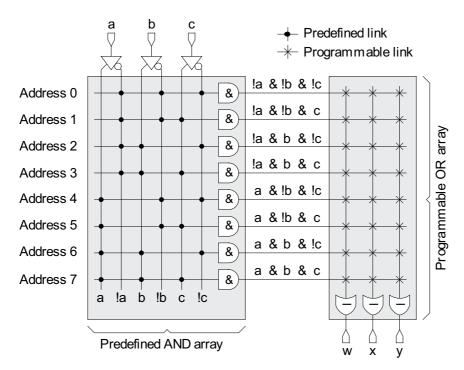

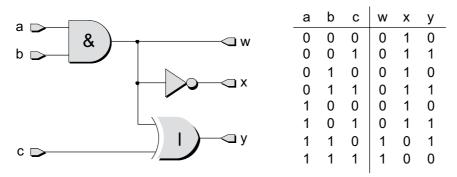

### VI.1.1 A Short History of Programmable Logic Devices

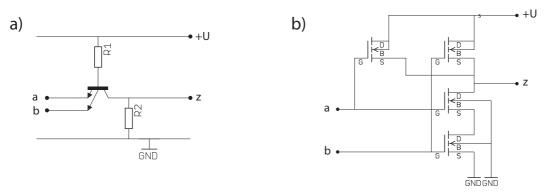

**Figure VI.1:** a) shows a TTL AND gate implemented using a multi emitter bipolar junction transistor. b) shows a NAND gate implemented in CMOS logic.

The history of modern digital electronics started with the invention of the transistor in 1947<sup>1</sup>. Only a short time later, the bipolar junction transistor was invented. Connecting several of these transistors, it is possible to create digital logic gates [Tietze83]. According to the way, in which the transistors are connected, the gates are classified either transistor-transistor logic (TTL) or emitter coupled logic (ECL). Logic gates build in ECL are faster than their TTL counterparts but also consume more power [Horowitz89].